PIC18F2420/2520/4420/4520 Enhanced Flash ... - Farnell - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-pmbta13_pmbt..> 15-Jul-2014 17:06 959K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EE-SPX303N-4..> 15-Jul-2014 17:06 969K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 15-Jul-2014 17:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MIDAS-un-tra..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SERIAL-TFT-M..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-series..> 15-Jul-2014 16:48 787K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-DC-Conver..> 15-Jul-2014 16:48 781K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:47 803K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMLM-Series-..> 15-Jul-2014 16:47 810K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEL-5-Series..> 15-Jul-2014 16:47 814K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TXL-series-t..> 15-Jul-2014 16:47 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEP-150WI-Se..> 15-Jul-2014 16:47 837K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AC-DC-Power-..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-Instruct..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TOS-tracopow..> 15-Jul-2014 16:47 852K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TCL-DC-traco..> 15-Jul-2014 16:46 858K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-series-t..> 15-Jul-2014 16:46 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-Series..> 15-Jul-2014 16:46 897K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-3-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEN-8-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:46 947K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HIP4081A-Int..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ISL6251-ISL6..> 07-Jul-2014 19:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DG411-DG412-..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3367-ARALDIT..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ICM7228-Inte..> 07-Jul-2014 19:46 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-K..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Silica-Gel-M..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TKC2-Dusters..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CRC-HANDCLEA..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-760G-French-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Decapant-KF-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1734-ARALDIT..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Araldite-Fus..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fiche-de-don..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-safety-data-..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-4-Hardener..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC-Debugger-..> 07-Jul-2014 19:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430-Hardw..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SmartRF06-Ev..> 07-Jul-2014 19:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2531-USB-H..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK889B-PONT-..> 07-Jul-2014 19:42 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-User-Guide-M..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 07-Jul-2014 19:41 2.0M

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

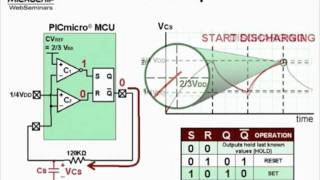

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 16-Jul-2014 09:04 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 16-Jul-2014 09:04 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-Full-N..> 16-Jul-2014 09:03 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S4011_402..> 16-Jul-2014 09:03 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC408x-7x 3..> 16-Jul-2014 09:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PCF8574-PCF8..> 16-Jul-2014 09:03 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-32-b..> 16-Jul-2014 09:02 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 16-Jul-2014 09:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC3220-30-4..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC11U3x-32-..> 16-Jul-2014 09:01 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3ICS1002-1..> 16-Jul-2014 09:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 08-Jul-2014 18:59 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-tesa®pack63..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Encodeur-USB..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2530ZDK-Us..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2020-Manuel-..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Synchronous-..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Arithmetic-L..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-4-Bit-Magnit..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM555-Timer-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293d-Texas-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC244-SN..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX232-MAX23..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-High-precisi..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMU-Instrume..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-900-Series-B..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BA-Series-Oh..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-270-Series-O..> 08-Jul-2014 18:49 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tiva-C-Serie..> 08-Jul-2014 18:49 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTO-Souriau-..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Clipper-Seri..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOURIAU-Cont..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-851-Series-P..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 06-Jul-2014 10:06 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7171-16-Bi..> 06-Jul-2014 10:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-Noise-24..> 06-Jul-2014 10:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:05 938K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74LCX573-Fai..> 06-Jul-2014 10:05 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1N4148WS-Fai..> 06-Jul-2014 10:04 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FAN6756-Fair..> 06-Jul-2014 10:04 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 06-Jul-2014 10:04 861K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES1F-ES1J-fi..> 06-Jul-2014 10:04 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-QRE1113-Fair..> 06-Jul-2014 10:03 879K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N7002DW-Fai..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDC2512-Fair..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDV301N-Digi..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S1A-Fairchil..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAV99-Fairch..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74AC00-74ACT..> 06-Jul-2014 10:03 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NaPiOn-Panas..> 06-Jul-2014 10:02 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LQ-RELAYS-AL..> 06-Jul-2014 10:02 924K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ev-relays-ae..> 06-Jul-2014 10:02 926K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:02 931K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplifier-In..> 06-Jul-2014 10:02 940K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serial-File-..> 06-Jul-2014 10:02 941K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Both-the-Del..> 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Videk-PDF.htm 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

© 2007 Microchip Technology Inc. Preliminary DS39631B

PIC18F2420/2520/4420/4520

Data Sheet

Enhanced Flash Microcontrollers

with 10-Bit A/D and nanoWatt Technology

DS39631B-page ii Preliminary © 2007 Microchip Technology Inc.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART,

PRO MATE, PowerSmart, rfPIC and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB,

SEEVAL, SmartSensor and The Embedded Control Solutions

Company are registered trademarks of Microchip Technology

Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, ECAN,

ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,

In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active

Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit,

PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal,

PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB,

rfPICDEM, Select Mode, Smart Serial, SmartTel, Total

Endurance, UNI/O, WiperLock and ZENA are trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2007, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona, Gresham, Oregon and Mountain View, California. The

Company’s quality system processes and procedures are for its PIC®

MCUs and dsPIC DSCs, KEELOQ® code hopping devices, Serial

EEPROMs, microperipherals, nonvolatile memory and analog

products. In addition, Microchip’s quality system for the design and

manufacture of development systems is ISO 9001:2000 certified.

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 1

PIC18F2420/2520/4420/4520

Power Managed Modes:

• Run: CPU on, peripherals on

• Idle: CPU off, peripherals on

• Sleep: CPU off, peripherals off

• Idle mode currents down to 5.8 μA typical

• Sleep mode current down to 0.1 μA typical

• Timer1 Oscillator: 1.8 μA, 32 kHz, 2V

• Watchdog Timer: 2.1 μA

• Two-Speed Oscillator Start-up

Peripheral Highlights:

• High-current sink/source 25 mA/25 mA

• Three programmable external interrupts

• Four input change interrupts

• Up to 2 Capture/Compare/PWM (CCP) modules,

one with Auto-Shutdown (28-pin devices)

• Enhanced Capture/Compare/PWM (ECCP)

module (40/44-pin devices only):

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-Shutdown and Auto-Restart

• Master Synchronous Serial Port (MSSP) module

supporting 3-wire SPI™ (all 4 modes) and I2C™

Master and Slave Modes

• Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN 1.2

- RS-232 operation using internal oscillator

block (no external crystal required)

- Auto-Wake-up on Start bit

- Auto-Baud Detect

• 10-bit, up to 13-channel Analog-to-Digital

Converter module (A/D):

- Auto-acquisition capability

- Conversion available during Sleep

• Dual analog comparators with input multiplexing)

Flexible Oscillator Structure:

• Four Crystal modes, up to 40 MHz

• 4X Phase Lock Loop (available for crystal and

internal oscillators)

• Two External RC modes, up to 4 MHz

• Two External Clock modes, up to 40 MHz

• Internal oscillator block:

- 8 user selectable frequencies, from 31 kHz to 8 MHz

- Provides a complete range of clock speeds

from 31 kHz to 32 MHz when used with PLL

- User tunable to compensate for frequency drift

• Secondary oscillator using Timer1 @ 32 kHz

• Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

Special Microcontroller Features:

• C compiler optimized architecture:

- Optional extended instruction set designed to

optimize re-entrant code

• 100,000 erase/write cycle Enhanced Flash

program memory typical

• 1,000,000 erase/write cycle Data EEPROM

memory typical

• Flash/Data EEPROM Retention: 100 years typical

• Self-programmable under software control

• Priority levels for interrupts

• 8 x 8 Single-Cycle Hardware Multiplier

• Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

• Single-supply 5V In-Circuit Serial

Programming™ (ICSP™) via two pins

• In-Circuit Debug (ICD) via two pins

• Wide operating voltage range: 2.0V to 5.5V

• Programmable 16-level High/Low-Voltage

Detection (HLVD) module:

- Supports interrupt on High/Low-Voltage

Detection

• Programmable Brown-out Reset (BOR

- With software enable option

28/40/44-Pin Enhanced Flash Microcontrollers with

10-Bit A/D and nanoWatt Technology

PIC18F2420/2520/4420/4520

DS39631B-page 2 Preliminary © 2007 Microchip Technology Inc.

-

Device

Program Memory Data Memory

I/O

10-bit

A/D (ch)

CCP/

ECCP

(PWM)

MSSP

EUSART

Comp.

Timers

Flash 8/16-bit

(bytes)

# Single-Word

Instructions

SRAM

(bytes)

EEPROM

(bytes)

SPI

Master

I2C

PIC18F2420 16K 8192 768 256 25 10 2/0 Y Y 1 2 1/3

PIC18F2520 32K 16384 1536 256 25 10 2/0 Y Y 1 2 1/3

PIC18F4420 16K 8192 768 256 36 13 1/1 Y Y 1 2 1/3

PIC18F4520 32K 16384 1536 256 36 13 1/1 Y Y 1 2 1/3

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 3

PIC18F2420/2520/4420/4520

Pin Diagrams

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/KBI0/AN11

RB3/AN9/CCP2(1)

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

VDD

VSS

RD7/PSP7/P1D

RD6/PSP6/P1C

RD5/PSP5/P1B

RD4/PSP4

RC7/RX/DT

RC6/TX/CK

RC5/SDO

RC4/SDI/SDA

RD3/PSP3

RD2/PSP2

MCLR/VPP/RE3

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/HLVDIN/C2OUT

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

VDD

VSS

OSC1/CLKI/RA7

OSC2/CLKO/RA6

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2(1)

RC2/CCP1/P1A

RC3/SCK/SCL

RD0/PSP0

RD1/PSP1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

PIC18F4520 PIC18F2520

10

11

2

3

4

5

6

1

8

7

9

12

13

14 15

16

17

18

19

20

23

24

25

26

27

28

22

21

MCLR/VPP/RE3

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/HLVDIN/C2OUT

VSS

OSC1/CLKI/RA7

OSC2/CLKO/RA6

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2(1)

RC2/CCP1

RC3/SCK/SCL

RB7/KBI3/PGD

RB6//KBI2/PGC

RB5/KBI1/PGM

RB4/KBI0/AN11

RB3/AN9/CCP2(1)

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

VDD

VSS

RC7/RX/DT

RC6/TX/CK

RC5/SDO

RC4/SDI/SDA

40-pin PDIP

28-pin PDIP, SOIC

PIC18F4420 PIC18F2420

Note 1: RB3 is the alternate pin for CCP2 multiplexing.

1011

2

3

6

1

18

19

20

21

22

12 13 14

15

8

7

16

17

2827 2625 2423

9

PIC18F2420

RC0/T1OSO/T13CKI

5

4

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4KBI0/AN11

RB3/AN9/CCP2(1)

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

VDD

VSS

RC7/RX/DT

RC6/TX/CK

RC5/SDO

RC4/SDI/SDA

MCLR/VPP/RE3

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/HLVDIN/C2OUT

VSS

OSC1/CLKI/RA7

OSC2/CLKO/RA6

RC1/T1OSI/CCP2(1)

RC2/CCP1

RC3/SCK/SCL

PIC18F2520

28-pin QFN

PIC18F2420/2520/4420/4520

DS39631B-page 4 Preliminary © 2007 Microchip Technology Inc.

Pin Diagrams (Cont.’d)

Note 1: RB3 is the alternate pin for CCP2 multiplexing.

10

11

2

345

6

1

18

19

20

21

22

12

13

14

15

38

8 7

44

43

42

41

40

39

16

17

29

30

31

32

33

23

24

25

26

27

28

36

34

35

9

PIC18F4420

37

RA3/AN3/VREF+

RA2/AN2/VREF-/CVREF

RA1/AN1

RA0/AN0

MCLR/VPP/RE3

RB3/AN9/CCP2(1)

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/KBI0/AN11

NC

RC6/TX/CK

RC5/SDO

RC4/SDI/SDA

RD3/PSP3

RD2/PSP2

RD1/PSP1

RD0/PSP0

RC3/SCK/SCL

RC2/CCP1/P1A

RC1/T1OSI/CCP2(1)

RC0/T1OSO/T13CKI

OSC2/CLKO/RA6

OSC1/CLKI/RA7

VSS

VSS

VDD

VDD

RE2/CS/AN7

RE1/WR/AN6

RE0/RD/AN5

RA5/AN4/SS/HLVDIN/C2OUT

RA4/T0CKI/C1OUT

RC7/RX/DT

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

VSS

VDD

VDD

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

44-pin QFN

PIC18F4520

10

11

2

345

6

1

18

19

20

21

22

12

13

14

15

38

8 7

44

43

42

41

40

39

16

17

29

30

31

32

33

23

24

25

26

27

28

36

34

35

9

PIC18F4420

37

RA3/AN3/VREF+

RA2/AN2/VREF-/CVREF

RA1/AN1

RA0/AN0

MCLR/VPP/RE3

NC

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/KBI0/AN11

NC

RC6/TX/CK

RC5/SDO

RC4/SDI/SDA

RD3/PSP3

RD2/PSP2

RD1/PSP1

RD0/PSP0

RC3/SCK/SCL

RC2/CCP1/P1A

RC1/T1OSI/CCP2(1)

NC

NC

RC0/T1OSO/T13CKI

OSC2/CLKO/RA6

OSC1/CLKI/RA7

VSS

VDD

RE2/CS/AN7

RE1/WR/AN6

RE0/RD/AN5

RA5/AN4/SS/HLVDIN/C2OUT

RA4/T0CKI/C1OUT

RC7/RX/DT

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

VSS

VDD

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

RB3/AN9/CCP2(1)

44-pin TQFP

PIC18F4520

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 5

PIC18F2420/2520/4420/4520

Table of Contents

1.0 Device Overview .......................................................................................................................................................................... 7

2.0 Oscillator Configurations ............................................................................................................................................................ 23

3.0 Power Managed Modes ............................................................................................................................................................. 33

4.0 Reset .......................................................................................................................................................................................... 41

5.0 Memory Organization................................................................................................................................................................. 53

6.0 Flash Program Memory.............................................................................................................................................................. 73

7.0 Data EEPROM Memory ............................................................................................................................................................. 83

8.0 8 x 8 Hardware Multiplier............................................................................................................................................................ 89

9.0 Interrupts .................................................................................................................................................................................... 91

10.0 I/O Ports ................................................................................................................................................................................... 105

11.0 Timer0 Module ......................................................................................................................................................................... 123

12.0 Timer1 Module ......................................................................................................................................................................... 127

13.0 Timer2 Module ......................................................................................................................................................................... 133

14.0 Timer3 Module ......................................................................................................................................................................... 135

15.0 Capture/Compare/Pwm (CCP) Modules .................................................................................................................................. 139

16.0 Enhanced Capture/Compare/PWM (ECCP) Module................................................................................................................ 147

17.0 Master Synchronous Serial Port (MSSP) Module .................................................................................................................... 161

18.0 Enhanced Universal Synchronous Receiver Transmitter (EUSART)....................................................................................... 201

19.0 10-Bit Analog-to-Digital Converter (A/D) Module ..................................................................................................................... 223

20.0 Comparator Module.................................................................................................................................................................. 233

21.0 Comparator Voltage Reference Module................................................................................................................................... 239

22.0 High/Low-Voltage Detect (HLVD)............................................................................................................................................. 243

23.0 Special Features of the CPU.................................................................................................................................................... 249

24.0 Instruction Set Summary .......................................................................................................................................................... 267

25.0 Development Support............................................................................................................................................................... 317

26.0 Electrical Characteristics .......................................................................................................................................................... 323

27.0 DC and AC Characteristics Graphs and Tables....................................................................................................................... 361

28.0 Packaging Information.............................................................................................................................................................. 363

Appendix A: Revision History............................................................................................................................................................. 371

Appendix B: Device Differences ........................................................................................................................................................ 371

Appendix C: Conversion Considerations ........................................................................................................................................... 372

Appendix D: Migration from Baseline to Enhanced Devices.............................................................................................................. 372

Appendix E: Migration from Mid-Range to Enhanced Devices .......................................................................................................... 373

Appendix F: Migration from High-End to Enhanced Devices............................................................................................................. 373

Index .................................................................................................................................................................................................. 375

On-Line Support................................................................................................................................................................................. 385

Systems Information and Upgrade Hot Line ...................................................................................................................................... 385

Reader Response .............................................................................................................................................................................. 386

PIC18F2420/2520/4420/4520 Product Identification System ............................................................................................................ 387

PIC18F2420/2520/4420/4520

DS39631B-page 6 Preliminary © 2007 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 7

PIC18F2420/2520/4420/4520

1.0 DEVICE OVERVIEW

This document contains device specific information for

the following devices:

This family offers the advantages of all PIC18 microcontrollers

– namely, high computational performance

at an economical price – with the addition of highendurance,

Enhanced Flash program memory. On top

of these features, the PIC18F2420/2520/4420/4520

family introduces design enhancements that make

these microcontrollers a logical choice for many highperformance,

power sensitive applications.

1.1 New Core Features

1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2420/2520/4420/4520

family incorporate a range of features that can significantly

reduce power consumption during operation.

Key items include:

• Alternate Run Modes: By clocking the controller

from the Timer1 source or the internal oscillator

block, power consumption during code execution

can be reduced by as much as 90%.

• Multiple Idle Modes: The controller can also run

with its CPU core disabled but the peripherals still

active. In these states, power consumption can be

reduced even further, to as little as 4% of normal

operation requirements.

• On-the-fly Mode Switching: The power

managed modes are invoked by user code during

operation, allowing the user to incorporate powersaving

ideas into their application’s software

design.

• Low Consumption in Key Modules: The

power requirements for both Timer1 and the

Watchdog Timer are minimized. See

Section 26.0 “Electrical Characteristics”

for values.

1.1.2 MULTIPLE OSCILLATOR OPTIONS

AND FEATURES

All of the devices in the PIC18F2420/2520/4420/4520

family offer ten different oscillator options, allowing

users a wide range of choices in developing application

hardware. These include:

• Four Crystal modes, using crystals or ceramic

resonators

• Two External Clock modes, offering the option of

using two pins (oscillator input and a divide-by-4

clock output) or one pin (oscillator input, with the

second pin reassigned as general I/O)

• Two External RC Oscillator modes with the same

pin options as the External Clock modes

• An internal oscillator block which provides an

8 MHz clock and an INTRC source (approximately

31 kHz), as well as a range of 6 user

selectable clock frequencies, between 125 kHz to

4 MHz, for a total of 8 clock frequencies. This

option frees the two oscillator pins for use as

additional general purpose I/O.

• A Phase Lock Loop (PLL) frequency multiplier,

available to both the high-speed crystal and internal

oscillator modes, which allows clock speeds of

up to 40 MHz. Used with the internal oscillator, the

PLL gives users a complete selection of clock

speeds, from 31 kHz to 32 MHz – all without using

an external crystal or clock circuit.

Besides its availability as a clock source, the internal

oscillator block provides a stable reference source that

gives the family additional features for robust

operation:

• Fail-Safe Clock Monitor: This option constantly

monitors the main clock source against a reference

signal provided by the internal oscillator. If a

clock failure occurs, the controller is switched to

the internal oscillator block, allowing for continued

low-speed operation or a safe application

shutdown.

• Two-Speed Start-up: This option allows the

internal oscillator to serve as the clock source

from Power-on Reset, or wake-up from Sleep

mode, until the primary clock source is available.

• PIC18F2420 • PIC18LF2420

• PIC18F2520 • PIC18LF2520

• PIC18F4420 • PIC18LF4420

• PIC18F4520 • PIC18LF4520

PIC18F2420/2520/4420/4520

DS39631B-page 8 Preliminary © 2007 Microchip Technology Inc.

1.2 Other Special Features

• Memory Endurance: The Enhanced Flash cells

for both program memory and data EEPROM are

rated to last for many thousands of erase/write

cycles – up to 100,000 for program memory and

1,000,000 for EEPROM. Data retention without

refresh is conservatively estimated to be greater

than 40 years.

• Self-programmability: These devices can write

to their own program memory spaces under internal

software control. By using a bootloader routine

located in the protected Boot Block at the top

of program memory, it becomes possible to create

an application that can update itself in the field.

• Extended Instruction Set: The PIC18F2420/

2520/4420/4520 family introduces an optional

extension to the PIC18 instruction set, which adds

8 new instructions and an Indexed Addressing

mode. This extension, enabled as a device configuration

option, has been specifically designed

to optimize re-entrant application code originally

developed in high-level languages, such as C.

• Enhanced CCP module: In PWM mode, this

module provides 1, 2 or 4 modulated outputs for

controlling half-bridge and full-bridge drivers.

Other features include Auto-Shutdown, for disabling

PWM outputs on interrupt or other select

conditions and Auto-Restart, to reactivate outputs

once the condition has cleared.

• Enhanced Addressable USART: This serial

communication module is capable of standard

RS-232 operation and provides support for the LIN

bus protocol. Other enhancements include

automatic baud rate detection and a 16-bit Baud

Rate Generator for improved resolution. When the

microcontroller is using the internal oscillator

block, the USART provides stable operation for

applications that talk to the outside world without

using an external crystal (or its accompanying

power requirement).

• 10-bit A/D Converter: This module incorporates

programmable acquisition time, allowing for a

channel to be selected and a conversion to be

initiated without waiting for a sampling period and

thus, reduce code overhead.

• Extended Watchdog Timer (WDT): This

enhanced version incorporates a 16-bit prescaler,

allowing an extended time-out range that is stable

across operating voltage and temperature. See

Section 26.0 “Electrical Characteristics” for

time-out periods.

1.3 Details on Individual Family

Members

Devices in the PIC18F2420/2520/4420/4520 family are

available in 28-pin and 40/44-pin packages. Block

diagrams for the two groups are shown in Figure 1-1

and Figure 1-2.

The devices are differentiated from each other in five

ways:

1. Flash program memory (16 Kbytes for

PIC18F2420/4420 devices and 32 Kbytes for

PIC18F2520/4520).

2. A/D channels (10 for 28-pin devices, 13 for

40/44-pin devices).

3. I/O ports (3 bidirectional ports on 28-pin devices,

5 bidirectional ports on 40/44-pin devices).

4. CCP and Enhanced CCP implementation

(28-pin devices have 2 standard CCP modules,

40/44-pin devices have one standard CCP

module and one ECCP module).

5. Parallel Slave Port (present only on 40/44-pin

devices).

All other features for devices in this family are identical.

These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and

Table 1-3.

Like all Microchip PIC18 devices, members of the

PIC18F2420/2520/4420/4520 family are available as

both standard and low-voltage devices. Standard

devices with Enhanced Flash memory, designated with

an “F” in the part number (such as PIC18F2420),

accommodate an operating VDD range of 4.2V to 5.5V.

Low-voltage parts, designated by “LF” (such as

PIC18LF2420), function over an extended VDD range

of 2.0V to 5.5V.

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 9

PIC18F2420/2520/4420/4520

TABLE 1-1: DEVICE FEATURES

Features PIC18F2420 PIC18F2520 PIC18F4420 PIC18F4520

Operating Frequency DC – 40 MHz DC – 40 MHz DC – 40 MHz DC – 40 MHz

Program Memory (Bytes) 16384 32768 16384 32768

Program Memory

(Instructions)

8192 16384 8192 16384

Data Memory (Bytes) 768 1536 768 1536

Data EEPROM Memory (Bytes) 256 256 256 256

Interrupt Sources 19 19 20 20

I/O Ports Ports A, B, C, (E) Ports A, B, C, (E) Ports A, B, C, D, E Ports A, B, C, D, E

Timers 4 4 4 4

Capture/Compare/PWM Modules 2 2 1 1

Enhanced

Capture/Compare/PWM Modules

0 0 1 1

Serial Communications MSSP,

Enhanced USART

MSSP,

Enhanced USART

MSSP,

Enhanced USART

MSSP,

Enhanced USART

Parallel Communications (PSP) No No Yes Yes

10-bit Analog-to-Digital Module 10 Input Channels 10 Input Channels 13 Input Channels 13 Input Channels

Resets (and Delays) POR, BOR,

RESET Instruction,

Stack Full, Stack

Underflow (PWRT, OST),

MCLR (optional), WDT

POR, BOR,

RESET Instruction,

Stack Full, Stack

Underflow (PWRT, OST),

MCLR (optional), WDT

POR, BOR,

RESET Instruction,

Stack Full, Stack

Underflow (PWRT, OST),

MCLR (optional), WDT

POR, BOR,

RESET Instruction,

Stack Full, Stack

Underflow (PWRT, OST),

MCLR (optional), WDT

Programmable

High/Low-Voltage Detect

Yes Yes Yes Yes

Programmable Brown-out Reset Yes Yes Yes Yes

Instruction Set 75 Instructions;

83 with Extended

Instruction Set enabled

75 Instructions;

83 with Extended

Instruction Set enabled

75 Instructions;

83 with Extended

Instruction Set enabled

75 Instructions;

83 with Extended

Instruction Set enabled

Packages 28-pin PDIP

28-pin SOIC

28-pin QFN

28-pin PDIP

28-pin SOIC

28-pin QFN

40-pin PDIP

44-pin QFN

44-pin TQFP

40-pin PDIP

44-pin QFN

44-pin TQFP

PIC18F2420/2520/4420/4520

DS39631B-page 10 Preliminary © 2007 Microchip Technology Inc.

FIGURE 1-1: PIC18F2420/2520 (28-PIN) BLOCK DIAGRAM

Instruction

Decode and

Control

PORTA

PORTB

PORTC

RA4/T0CKI/C1OUT

RA5/AN4/SS/HLVDIN/C2OUT

RB0/INT0/FLT0/AN12

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2(1)

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RA3/AN3/VREF+

RA2/AN2/VREF-/CVREF

RA1/AN1

RA0/AN0

RB1/INT1/AN10

Data Latch

Data Memory

( 3.9 Kbytes )

Address Latch

Data Address<12>

12

BSR FSR0 Access

FSR1

FSR2

inc/dec

logic

Address

4 12 4

PCH PCL

PCLATH

8

31 Level Stack

Program Counter

PRODH PRODL

8 x 8 Multiply

8

BITOP

8 8

ALU<8>

Address Latch

Program Memory

(16/32 Kbytes)

Data Latch

20

8

8

Table Pointer<21>

inc/dec logic

21

8

Data Bus<8>

Table Latch

8

IR

12

3

ROM Latch

RB2/INT2/AN8

RB3/AN9/CCP2(1)

PCLATU

PCU

OSC2/CLKO(3)/RA6

Note 1: CCP2 is multiplexed with RC1 when configuration bit CCP2MX is set, or RB3 when CCP2MX is not set.

2: RE3 is only available when MCLR functionality is disabled.

3: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O.

Refer to Section 2.0 “Oscillator Configurations” for additional information.

RB4/KBI0/AN11

RB5/KBI1/PGM

RB6/KBI2/PGC

RB7/KBI3/PGD

Comparator MSSP EUSART 10-bit

ADC

Timer0 Timer1 Timer2 Timer3

CCP2

HLVD

CCP1

BOR Data

EEPROM

W

Instruction Bus <16>

STKPTR Bank

8

State machine

control signals

Decode

8

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

OSC1(3)

OSC2(3)

VDD,

Brown-out

Reset

Internal

Oscillator

Fail-Safe

Clock Monitor

Precision

Reference

Band Gap

VSS

MCLR(2)

Block

INTRC

Oscillator

8 MHz

Oscillator

Single-Supply

Programming

In-Circuit

Debugger

T1OSO

OSC1/CLKI(3)/RA7

T1OSI

PORTE

MCLR/VPP/RE3(2)

© 2007 Microchip Technology Inc. Preliminary DS39631B-page 11

PIC18F2420/2520/4420/4520

FIGURE 1-2: PIC18F4420/4520 (40/44-PIN) BLOCK DIAGRAM

Instruction

Decode and

Control

Data Latch

Data Memory

( 3.9 Kbytes )

Address Latch

Data Address<12>

12

BSR FSR0 Access

FSR1

FSR2

inc/dec

logic

Address

4 12 4

PCH PCL

PCLATH

8

31 Level Stack

Program Counter

PRODH PRODL

8 x 8 Multiply

8

BITOP

8 8

ALU<8>

Address Latch

Program Memory

(16/32 Kbytes)

Data Latch

20

8

8

Table Pointer<21>

inc/dec logic

21

8

Data Bus<8>

Table Latch

8

IR

12

3

ROM Latch

PORTD

RD0/PSP0

PCLATU

PCU

PORTE

MCLR/VPP/RE3(2)

RE2/CS/AN7

RE0/RD/AN5

RE1/WR/AN6

Note 1: CCP2 is multiplexed with RC1 when configuration bit CCP2MX is set, or RB3 when CCP2MX is not set.

2: RE3 is only available when MCLR functionality is disabled.

3: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O.

Refer to Section 2.0 “Oscillator Configurations” for additional information.

:RD4/PSP4

Comparator MSSP EUSART 10-bit

ADC