TEXAS INSTRUMENTS - Highly Integrated Digital Controller for Isolated Power (Rev. B) - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

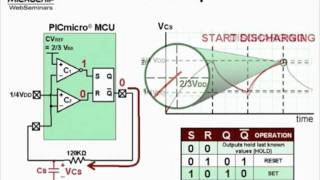

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-pmbta13_pmbt..> 15-Jul-2014 17:06 959K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EE-SPX303N-4..> 15-Jul-2014 17:06 969K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 15-Jul-2014 17:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MIDAS-un-tra..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SERIAL-TFT-M..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-series..> 15-Jul-2014 16:48 787K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-DC-Conver..> 15-Jul-2014 16:48 781K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:47 803K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMLM-Series-..> 15-Jul-2014 16:47 810K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEL-5-Series..> 15-Jul-2014 16:47 814K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TXL-series-t..> 15-Jul-2014 16:47 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEP-150WI-Se..> 15-Jul-2014 16:47 837K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AC-DC-Power-..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-Instruct..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TOS-tracopow..> 15-Jul-2014 16:47 852K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TCL-DC-traco..> 15-Jul-2014 16:46 858K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-series-t..> 15-Jul-2014 16:46 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-Series..> 15-Jul-2014 16:46 897K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-3-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEN-8-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:46 947K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HIP4081A-Int..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ISL6251-ISL6..> 07-Jul-2014 19:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DG411-DG412-..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3367-ARALDIT..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ICM7228-Inte..> 07-Jul-2014 19:46 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-K..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Silica-Gel-M..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TKC2-Dusters..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CRC-HANDCLEA..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-760G-French-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Decapant-KF-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1734-ARALDIT..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Araldite-Fus..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fiche-de-don..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-safety-data-..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-4-Hardener..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC-Debugger-..> 07-Jul-2014 19:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430-Hardw..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SmartRF06-Ev..> 07-Jul-2014 19:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2531-USB-H..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK889B-PONT-..> 07-Jul-2014 19:42 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-User-Guide-M..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mini-Fit-Jr-..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-43031-0002-M..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0433751001-D..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cube-3D-Prin..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-Compact-..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-3250-MTX..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 18-Jul-2014 17:00 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCP3421-Micr..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM19-Texas-I..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-S..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMH6518-Texa..> 18-Jul-2014 16:59 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7719-Low-V..> 18-Jul-2014 16:59 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DAC8143-Data..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BGA7124-400-..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SICK-OPTIC-E..> 18-Jul-2014 16:58 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT3757-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT1961-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2420-2..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DS3231-DS-PD..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RDS-80-PDF.htm 18-Jul-2014 16:57 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8300-Data-..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT6233-Linea..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX1365-MAX1..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPSAF5130-PD..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DP83846A-DsP..> 18-Jul-2014 16:55 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 18-Jul-2014 16:55 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 16-Jul-2014 09:04 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 16-Jul-2014 09:04 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-Full-N..> 16-Jul-2014 09:03 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S4011_402..> 16-Jul-2014 09:03 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC408x-7x 3..> 16-Jul-2014 09:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PCF8574-PCF8..> 16-Jul-2014 09:03 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-32-b..> 16-Jul-2014 09:02 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 16-Jul-2014 09:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC3220-30-4..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC11U3x-32-..> 16-Jul-2014 09:01 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3ICS1002-1..> 16-Jul-2014 09:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 08-Jul-2014 18:59 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-tesa®pack63..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Encodeur-USB..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2530ZDK-Us..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2020-Manuel-..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Synchronous-..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Arithmetic-L..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-4-Bit-Magnit..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM555-Timer-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293d-Texas-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC244-SN..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX232-MAX23..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-High-precisi..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMU-Instrume..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-900-Series-B..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BA-Series-Oh..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-270-Series-O..> 08-Jul-2014 18:49 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tiva-C-Serie..> 08-Jul-2014 18:49 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTO-Souriau-..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Clipper-Seri..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOURIAU-Cont..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-851-Series-P..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 06-Jul-2014 10:06 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7171-16-Bi..> 06-Jul-2014 10:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-Noise-24..> 06-Jul-2014 10:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:05 938K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74LCX573-Fai..> 06-Jul-2014 10:05 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1N4148WS-Fai..> 06-Jul-2014 10:04 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FAN6756-Fair..> 06-Jul-2014 10:04 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 06-Jul-2014 10:04 861K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES1F-ES1J-fi..> 06-Jul-2014 10:04 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-QRE1113-Fair..> 06-Jul-2014 10:03 879K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N7002DW-Fai..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDC2512-Fair..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDV301N-Digi..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S1A-Fairchil..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAV99-Fairch..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74AC00-74ACT..> 06-Jul-2014 10:03 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NaPiOn-Panas..> 06-Jul-2014 10:02 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LQ-RELAYS-AL..> 06-Jul-2014 10:02 924K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ev-relays-ae..> 06-Jul-2014 10:02 926K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:02 931K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplifier-In..> 06-Jul-2014 10:02 940K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serial-File-..> 06-Jul-2014 10:02 941K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Both-the-Del..> 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Videk-PDF.htm 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

UCD3138

Highly Integrated Digital Controller for Isolated Power

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SLUSAP2B

March 2012–Revised July 2012

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

Contents

1 Introduction ........................................................................................................................ 6

1.1 Features ...................................................................................................................... 6

1.2 Applications .................................................................................................................. 7

2 Overview ............................................................................................................................ 7

2.1 Description ................................................................................................................... 7

2.2 Ordering Information ........................................................................................................ 8

2.3 Product Selection Matrix ................................................................................................... 8

2.4 Functional Block Diagram .................................................................................................. 9

2.5 UCD3138 64 QFN – Pin Assignments ................................................................................. 10

2.6 Pin Functions .............................................................................................................. 11

2.7 UCD3138 40 QFN – Pin Assignments ................................................................................. 13

2.8 Pin Functions .............................................................................................................. 14

3 Electrical Specifications ..................................................................................................... 15

3.1 ABSOLUTE MAXIMUM RATINGS ...................................................................................... 15

3.2 THERMAL INFORMATION .............................................................................................. 15

3.3 RECOMMENDED OPERATING CONDITIONS ....................................................................... 15

3.4 ELECTRICAL CHARACTERISTICS .................................................................................... 16

3.5 PMBus/SMBus/I2C Timing ............................................................................................... 19

3.6 Power On Reset (POR) / Brown Out Reset (BOR) ................................................................... 20

3.7 Typical Clock Gating Power Savings ................................................................................... 21

3.8 Typical Temperature Characteristics ................................................................................... 22

4 Functional Overview .......................................................................................................... 23

4.1 ARM Processor ............................................................................................................ 23

4.2 Memory ..................................................................................................................... 23

4.2.1 CPU Memory Map and Interrupts ............................................................................ 23

4.2.1.1 Memory Map (After Reset Operation) ........................................................... 23

4.2.1.2 Memory Map (Normal Operation) ................................................................ 24

4.2.1.3 Memory Map (System and Peripherals Blocks) ................................................ 24

4.2.2 Boot ROM ....................................................................................................... 24

4.2.3 Customer Boot Program ....................................................................................... 25

4.2.4 Flash Management ............................................................................................. 25

4.3 System Module ............................................................................................................ 25

4.3.1 Address Decoder (DEC) ....................................................................................... 25

4.3.2 Memory Management Controller (MMC) .................................................................... 25

4.3.3 System Management (SYS) ................................................................................... 25

4.3.4 Central Interrupt Module (CIM) ............................................................................... 26

4.4 Peripherals ................................................................................................................. 27

4.4.1 Digital Power Peripherals ...................................................................................... 27

4.4.1.1 Front End ............................................................................................ 27

4.4.1.2 DPWM Module ..................................................................................... 28

4.4.1.3 DPWM Events ...................................................................................... 29

4.4.1.4 High Resolution DPWM ........................................................................... 31

4.4.1.5 Over Sampling ...................................................................................... 31

4.4.1.6 DPWM Interrupt Generation ...................................................................... 31

4.4.1.7 DPWM Interrupt Scaling/Range .................................................................. 31

4.5 DPWM Modes of Operation .............................................................................................. 32

4.5.1 Normal Mode .................................................................................................... 32

4.6 Phase Shifting ............................................................................................................. 34

4.7 DPWM Multiple Output Mode ............................................................................................ 35

4.8 DPWM Resonant Mode .................................................................................................. 36

4.9 Triangular Mode ........................................................................................................... 38

2 Contents Copyright © 2012, Texas Instruments Incorporated

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

4.10 Leading Edge Mode ....................................................................................................... 39

4.11 Sync FET Ramp and IDE Calculation .................................................................................. 41

4.12 Automatic Mode Switching ............................................................................................... 41

4.12.1 Phase Shifted Full Bridge Example .......................................................................... 41

4.12.2 LLC Example .................................................................................................... 42

4.12.3 Mechanism for Automatic Mode Switching .................................................................. 44

4.13 DPWMC, Edge Generation, IntraMux .................................................................................. 45

4.14 Filter ......................................................................................................................... 46

4.14.1 Loop Multiplexer ................................................................................................ 48

4.14.2 Fault Multiplexer ................................................................................................ 49

4.15 Communication Ports ..................................................................................................... 51

4.15.1 SCI (UART) Serial Communication Interface ............................................................... 51

4.15.2 PMBUS .......................................................................................................... 51

4.15.3 General Purpose ADC12 ...................................................................................... 52

4.15.4 Timers ............................................................................................................ 53

4.15.4.1 24-bit PWM Timer .................................................................................. 53

4.15.4.2 16-Bit PWM Timers ................................................................................ 54

4.15.4.3 Watchdog Timer .................................................................................... 54

4.16 Miscellaneous Analog ..................................................................................................... 54

4.17 Package ID Information ................................................................................................... 54

4.18 Brownout ................................................................................................................... 54

4.19 Global I/O ................................................................................................................... 55

4.20 Temperature Sensor Control ............................................................................................. 56

4.21 I/O Mux Control ............................................................................................................ 56

4.21.1 JTAG Use for I/O and JTAG Security ........................................................................ 57

4.22 Current Sharing Control .................................................................................................. 57

4.23 Temperature Reference .................................................................................................. 58

5 IC Grounding and Layout Recommendations ........................................................................ 59

6 Tools and Documentation ................................................................................................... 60

7 References ....................................................................................................................... 62

Revision History ......................................................................................................................... 63

Copyright © 2012, Texas Instruments Incorporated Contents 3

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

List of Figures

3-1 I2C/SMBus/PMBus Timing Diagram ........................................................................................... 20

3-2 Bus Timing in Extended Mode.................................................................................................. 20

3-3 Power On Reset (POR) / Brown Out Reset (BOR) .......................................................................... 20

3-4 EADC LSB Size with 4X Gain (mV) vs. Temperature ....................................................................... 22

3-5 ADC12 Measurement Temperature Sensor Voltage vs. Temperature.................................................... 22

3-6 ADC12 2.5-V Reference vs. Temperature .................................................................................... 22

3-7 ADC12 Temperature Sensor Measurement Error vs. Temperature....................................................... 22

3-8 UCD3138 Oscillator Frequency (2MHz Reference, Divided Down from 250MHz) vs. Temperature.................. 22

4-1 Input Stage of EADC Module ................................................................................................... 28

4-2 Front End Module ................................................................................................................ 28

4-3 Secondary-Referenced Phase-Shifted Full Bridge Control

With Synchronous Rectification ................................................................................................ 42

4-4 Secondary-Referenced Half-Bridge Resonant LLC Control

With Synchronous Rectification ................................................................................................ 43

4-5 Fault Mux Block Diagram ....................................................................................................... 51

4-6 PMBus Address Detection Method ............................................................................................ 52

4-7 ADC12 Control Block Diagram ................................................................................................. 53

4-8 Internal Temp Sensor............................................................................................................ 56

4-9 Simplified Current Sharing Circuitry ........................................................................................... 57

4 List of Figures Copyright © 2012, Texas Instruments Incorporated

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

List of Tables

2-1 Pin Functions ..................................................................................................................... 11

2-2 Pin Functions ..................................................................................................................... 14

3-1 I2C/SMBus/PMBus Timing Characteristics.................................................................................... 19

4-1 Interrupt Priority Table ........................................................................................................... 26

4-2 DPWM Interrupt Divide Ratio ................................................................................................... 31

Copyright © 2012, Texas Instruments Incorporated List of Tables 5

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

Highly Integrated Digital Controller for Isolated Power

Check for Samples: UCD3138

1 Introduction

1.1 Features

1

• Digital Control of up to 3 Independent – Synchronous Rectifier Soft On/Off

Feedback Loops – Low IC Standby Power

– Dedicated PID based hardware • Soft Start / Stop with and without Pre-bias

– 2-pole/2-zero configurable • Fast Input Voltage Feed Forward Hardware

– Non-Linear Control • Primary Side Voltage Sensing

• Up to 16MHz Error Analog to Digital Converter • Copper Trace Current Sensing

(EADC) • Flux and Phase Current Balancing for Non-

– Configurable Resolution as Small as Peak Current Mode Control Applications

1mV/LSB • Current Share Bus Support

– Automatic Resolution Selection – Analog Average

– Up to 8x Oversampling – Master/Slave

– Hardware Based Averaging (up to 8x) • Feature Rich Fault Protection Options

– 14 bit Effective DAC – 7 High Speed Analog Comparators

– Adaptive Sample Trigger Positioning – Cycle-by-Cycle Current Limiting

• Up to 8 High Resolution Digital Pulse Width – Programmable Fault Counting

Modulated (DPWM) Outputs – External Fault Inputs

– 250ps Pulse Width Resolution – 10 Digital Comparators

– 4ns Frequency Resolution – Programmable blanking time

– 4ns Phase Resolution • Synchronization of DPWM waveforms between

– Adjustable Phase Shift Between Outputs multiple UCD3138 devices

– Adjustable Dead-band Between Pairs • 14 channel, 12 bit, 267 ksps General Purpose

– Cycle-by-Cycle Duty Cycle Matching ADC with integrated

– Up to 2MHz Switching Frequency – Programmable averaging filters

• Configurable PWM Edge Movement – Dual sample and hold

– Trailing Modulation • Internal Temperature Sensor

– Leading Modulation • Fully Programmable High-Performance

– Triangular Modulation 31.25MHz, 32-bit ARM7TDMI-S Processor

• Configurable Feedback Control – 32 kByte (kB) Program Flash

– Voltage Mode – 2 kB Data Flash with ECC

– Average Current Mode – 4 kB Data RAM

– Peak Current Mode Control – 4 kB Boot ROM Enables Firmware Boot-Load

– Constant Current in the Field via I2C or UART

– Constant Power • Communication Peripherals

• Configurable Modulation Methods – I2C/PMBus

– Frequency Modulation – 2 UARTs on UCD3138RGC (64-pin QFN)

– Phase Shift Modulation – 1 UART on UCD3138RHA (40-pin QFN)

– Pulse Width Modulation • JTAG Debug Port

• Fast, Automatic and Smooth Mode Switching • Timer capture with selectable input pins

– Frequency Modulation and PWM • Up to 5 Additional General Purpose Timers

– Phase Shift Modulation and PWM • Built In Watchdog: BOD and POR

• High Efficiency and Light Load Management • 64-pin QFN and 40-pin QFN packages

– Burst Mode • Operating Temperature: –40°C to 125°C

– Ideal Diode Emulation • Fusion_Digital_Power_Designer GUI Support 1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 2012, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date. Products conform to

specifications per the terms of the Texas Instruments standard warranty. Production

processing does not necessarily include testing of all parameters.

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

1.2 Applications

• Power Supplies and Telecom Rectifiers

• Power Factor Correction

• Isolated dc-dc Modules

2 Overview

2.1 Description

The UCD3138 is a digital power supply controller from Texas Instruments offering superior levels of

integration and performance in a single chip solution. The flexible nature of the UCD3138 makes it

suitable for a wide variety of power conversion applications. In addition, multiple peripherals inside the

device have been specifically optimized to enhance the performance of ac/dc and isolated dc/dc

applications and reduce the solution component count in the IT and network infrastructure space.

The UCD3138 is a fully programmable solution offering customers complete control of their application,

along with ample ability to differentiate their solution. At the same time, TI is committed to simplifying our

customer’s development effort through offering best in class development tools, including application

firmware, Code Composer Studio™ software development environment, and TI’s power development GUI

which enables customers to configure and monitor key system parameters.

At the core of the UCD3138 controller are the digital control loop peripherals, also known as Digital Power

Peripherals (DPP). Each DPP implements a high speed digital control loop consisting of a dedicated Error

Analog to Digital Converter (EADC), a PID based 2 pole–2 zero digital compensator and DPWM outputs

with 250 ps pulse width resolution. The device also contains a 12-bit, 267ksps general purpose ADC with

up to 14 channels, timers, interrupt control, JTAG debug and PMBus and UART communications ports.

The device is based on a 32-bit ARM7TDMI-S RISC microcontroller that performs real-time monitoring,

configures peripherals and manages communications. The ARM microcontroller executes its program out

of programmable flash memory as well as on-chip RAM and ROM.

In addition to the FDPP, specific power management peripherals have been added to enable high

efficiency across the entire operating range, high integration for increased power density, reliability, and

lowest overall system cost and high flexibility with support for the widest number of control schemes and

topologies. Such peripherals include: light load burst mode, synchronous rectification, LLC and phase

shifted full bridge mode switching, input voltage feed forward, copper trace current sense, ideal diode

emulation, constant current constant power control, synchronous rectification soft on and off, peak current

mode control, flux balancing, secondary side input voltage sensing, high resolution current sharing,

hardware configurable soft start with pre bias, as well as several other features. Topology support has

been optimized for voltage mode and peak current mode controlled phase shifted full bridge, single and

dual phase PFC, bridgeless PFC, hard switched full bridge and half bridge, and LLC half bridge and full

bridge.

Copyright © 2012, Texas Instruments Incorporated Overview 7

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

2.2 Ordering Information

PART NUMBER PIN COUNT PACKAGE SUPPLY TOP SIDE MARKING OPERATING TEMPERATURE RANGE, TA

UCD3138RGCT 64 QFN 250 (Small Reel) UCD3138 –40°C to 125°C

UCD3138RGCR 64 QFN 2000 (Large Reel) UCD3138 –40°C to 125°C

UCD3138RHAT 40 QFN 250 (Small Reel) UCD3138 –40°C to 125°C

UCD3138RHAR 40 QFN 2500 (large Reel) UCD3138 –40°C to 125°C

2.3 Product Selection Matrix

FEATURE UCD3138 64 PIN UCD3138 40 PIN

ARM7TDMI-S Core Processor 31.25 MHz 31.25 MHz

High Resolution DPWM Outputs (250ps Resolution) 8 8

Number of High Speed Independent Feedback Loops (# Regulated Output 3 3 Voltages)

12-bit, 267ksps, General Purpose ADC Channels 14 7

Digital Comparators at ADC Outputs 4 4

Flash Memory (Program) 32 KB 32 KB

Flash Memory (Data) 2 KB 2 KB

Flash Security √ √

RAM 4 KB 4 KB

DPWM Switching Frequency up to 2 MHz up to 2 MHz

Programmable Fault Inputs 4 1 + 2(1)

High Speed Analog Comparators with Cycle-by-Cycle Current Limiting 7(2) 6(2)

UART (SCI) 2 1(1)

PMBus √ √

Timers 4 (16 bit) and 1 (24 bit) 4 (16 bit) and 1 (24 bit)

Timer PWM Outputs 2 1

Timer Capture Inputs 1 1(1)

Watchdog √ √

On Chip Oscillator √ √

Power-On Reset and Brown-Out Reset √ √

JTAG √ √

Package Offering 64 Pin QFN (9mm x 9mm) 40 Pin QFN (6mm x 6mm)

Sync IN and Sync OUT Functions √ √

Total GPIO (includes all pins with multiplexed functions such as, DPWM, Fault 30 18 Inputs, SCI, etc.)

External Interrupts 1 0

(1) This number represents an alternate pin out that is programmable via firmware. See the UCD3138 Digital Power Peripherals

Programmer’s Manual for details.

(2) To facilitate simple OVP and UVP connections both comparators B and C are connected to the AD03 pin.

8 Overview Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): UCD3138

Front End 2

Analog

Comparators

Power and

1.8 V Voltage

Regulator

AD07

AD06

AD04

V33DIO /RESET

SCI_RX0

SCI_TX0

PMBUS_CLK

PMBUS_DATA

AGND

V33D

BP18

FAULT3

FAULT2

TCAP

TMS

TDI

TDO

TCK

EXT_INT

FAULT1

FAULT0

PWM1

PWM0

SCI_RX1

SCI_TX1

PMBUS_CTRL

PMBUS_ALERT

SYNC

DGND

DPWM3B

DPWM3A

DPWM2B

DPWM2A

DPWM1B

DPWM1A

DPWM0B

DPWM0A

EAP0

EAN0

EAP1

EAN1

V33 A

AD00

AD01

AD0 2

AD1 3

PID Based

Filter 0

DPWM0

DPWM1

DPWM2

DPWM3

PID Based

Filter 1

PID Based

Filter 2

ADC_EXT_ TRIG

ADC12

ADC12 Control

Sequencing, Averaging,

Digital Compare, Dual

Sample and hold AD[13:0 ]

A

B

C

D

E

F

G

Current Share

Analog, Average, Master/Slave

AD03

AD0 2

AD1 3

AGND

PMBus

Timers

4 – 16 bit (PWM)

1 – 24 bit

UART0

UART1

GPIO

Control

JTAG

Loop MUX

ARM7TDMI-S

32 bit, 31.25 MHz

Memory

PFLASH 32 kB

DFLASH 2 kB

RAM 4 kB

ROM 4 kB

Power On Reset

Brown Out Detection

Oscillator

Internal Temperature

Sensor

Advanced Power Control

Mode Switching, Burst Mode, IDE,

Synchronous Rectification soft on & off

Front End 1

Constant Power Constant

Current

Input Voltage Feed Forward

Front End Averaging

Digital Comparators

Fault MUX &

Control

Cycle by Cycle

Current Limit

Digital

Comparators

DAC0

EADC

X

AFE

Value

Dither

!

CPCC

Filter x

Ramp

SAR/Prebias

Abs()

2 Avg() AFE

23-AFE

Peak Current Mode

Control Comparator

A0

EAP2

EAN2

Front End 0

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

2.4 Functional Block Diagram

Copyright © 2012, Texas Instruments Incorporated Overview 9

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

(64 QFN)

AGND 1

AD13 2

AD12 3

AD10 4

AD07 5

AD06 6

AD04 7

AD03 8

V33DIO 9

10

/RESET 11

ADC_EXT_TRIG/TCAP/SYNC/PWM0 12

SCI_RX0 13

SCI_TX0 14

DGND

PMBUS_CLK/SCI_TX0 15

PMBUS_DATA/SCI_RX0 16

48 AGND

47 V33D

46 BP18

45 V33DIO

44 DGND

43 FAULT3

42 FAULT2

41 TCAP

40 TMS

39 TDI/SCI_RX0/PMBUS_CTRL/FAULT1

38 TDO/SCI_TX0/PMBUS_ALERT/FAULT0

37 TCK/TCAP/SYNC/PWM0

36 FAULT1

35 FAULT0

34 INT_EXT

33 DGND

32

PWM1

31

PWM0

30

SCI_RX1/PMBUS_CTRL

29

SCI_TX1/PMBUS_ALERT

28

PMBUS_CTRL

27

PMBUS_ALERT

26

SYNC/TCAP/ADC_EXT_TRIG/PWM0

25

DGND

24

DPWM3B

23

DPWM3A

22

DPWM2B

21

DPWM2A

20

DPWM1B

19

DPWM1A

18

DPWM0B

17

DPWM0A

64

AGND

63

EAP0

62

EAN0

61

EAP1

60

EAN1

59

EAP2

58

EAN2

57

AGND

56

V33A

55

AD00

54

AD01

53

AD02

52

AD05

51

AD08

50

AD09

49

AD11

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

2.5 UCD3138 64 QFN – Pin Assignments

10 Overview Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

2.6 Pin Functions

Additional pin functionality is specified in the following table.

Table 2-1. Pin Functions

ALTERNATE ASSIGNMENT PIN NAME PRIMARY ASSIGNMENT CONFIGURABLE NO. 1 NO. 2 NO. 3 AS A GPIO?

1 AGND Analog ground

2 AD13 12-bit ADC, Ch 13, comparator E, I-share DAC output

3 AD12 12-bit ADC, Ch 12

4 AD10 12-bit ADC, Ch 10

5 AD07 12-bit ADC, Ch 7, Connected to comparator F and reference DAC output to comparator G

6 AD06 12-bit ADC, Ch 6, Connected to comparator F DAC output

7 AD04 12-bit ADC, Ch 4, Connected to comparator D DAC output

8 AD03 12-bit ADC, Ch 3, Connected to comparator B and C

9 V33DIO Digital I/O 3.3V core supply

10 DGND Digital ground

11 RESET Device Reset Input, active low

12 ADC_EXT_TRIG ADC conversion external trigger input TCAP SYNC PWM0 Yes

13 SCI_RX0 SCI RX 0 Yes

14 SCI_TX0 SCI TX 0 Yes

15 PMBUS_CLK PMBUS Clock (Open Drain) SCI TX 0 Yes

16 PMBUS_DATA PMBus data (Open Drain) SCI RX 0 Yes

17 DPWM0A DPWM 0A output Yes

18 DPWM0B DPWM 0B output Yes

19 DPWM1A DPWM 1A output Yes

20 DPWM1B DPWM 1B output Yes

21 DPWM2A DPWM 2A output Yes

22 DPWM2B DPWM 2B output Yes

23 DPWM3A DPWM 3A output Yes

24 DPWM3B DPWM 3B output Yes

25 DGND Digital ground

26 SYNC DPWM Synchronize pin TCAP ADC_EXT_ PWM0 Yes TRIG

27 PMBUS_ALERT PMBus Alert (Open Drain) Yes

28 PMBUS_CTRL PMBus Control (Open Drain) Yes

29 SCI_TX1 SCI TX 1 PMBUS_AL Yes ERT

30 SCI_RX1 SCI RX 1 PMBUS_CT Yes RL

31 PWM0 General purpose PWM 0 Yes

32 PWM1 General purpose PWM 1 Yes

33 DGND Digital ground

34 INT_EXT External Interrupt Yes

35 FAULT0 External fault input 0 Yes

36 FAULT1 External fault input 1 Yes

37 TCK JTAG TCK TCAP SYNC PWM0 Yes

38 TDO JTAG TDO SCI_TX0 PMBUS_AL FAULT0 Yes ERT

39 TDI JTAG TDI SCI_RX0 PMBUS_CT FAULT1 Yes RL

40 TMS JTAG TMS Yes

41 TCAP Timer capture input Yes

42 FAULT2 External fault input 2 Yes

43 FAULT3 External fault input 3 Yes

Copyright © 2012, Texas Instruments Incorporated Overview 11

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

Table 2-1. Pin Functions (continued)

ALTERNATE ASSIGNMENT PIN NAME PRIMARY ASSIGNMENT CONFIGURABLE NO. 1 NO. 2 NO. 3 AS A GPIO?

44 DGND Digital ground

45 V33DIO Digital I/O 3.3V core supply

46 BP18 1.8V Bypass

47 V33D Digital 3.3V core supply

48 AGND Substrate analog ground

49 AGND Analog ground

50 EAP0 Channel #0, differential analog voltage, positive input

51 EAN0 Channel #0, differential analog voltage, negative input

52 EAP1 Channel #1, differential analog voltage, positive input

53 EAN1 Channel #1, differential analog voltage, negative input

54 EAP2 Channel #2, differential analog voltage, positive input

55 EAN2 Channel #2, differential analog voltage, negative input

56 AGND Analog ground

57 V33A Analog 3.3V supply

58 AD00 12-bit ADC, Ch 0, Connected to current source

59 AD01 12-bit ADC, Ch 1, Connected to current source

60 AD02 12-bit ADC, Ch 2, Connected to comparator A, I-share

61 AD05 12-bit ADC, Ch 5

62 AD08 12-bit ADC, Ch 8

63 AD09 12-bit ADC, Ch 9

64 AD11 12-bit ADC, Ch 11

12 Overview Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

(40 QFN)

AGND 1

2

3

4

5

AD13

6

AD06

7

AD04

8

AD03

9

DGND

10

/RESET

11

ADC_EXT_TRIG/TCAP/SYNC/PWM0

12 13 14 15

PMBUS_CLK/SCI_TX0

16

PMBUS_DATA/SCI_RX0

AGND

BP18

DGND

V33D

40 39

TMS

38

TDI/SCI_RX0/PMBUS_CTRL/FAULT1

37

TDO/SCI_TX0/PMBUS_ALERT/FAULT0

36

TCK/TCAP/SYNC/PWM0

35 34 33

FAULT2

32 31

AGND

30

29

28

27

26

DPWM3B

25

DPWM3A

24

PMBUS_CTRL

23

PMBUS_ALERT

22

DPWM2B

21

DPWM2A

20

DPWM1B

19

DPWM1A

18

DPWM0B

17

DPWM0A

EAP0

EAN0

EAP1

EAN1

EAP2

AGND

V33A

AD00

AD01

AD02

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

2.7 UCD3138 40 QFN – Pin Assignments

Copyright © 2012, Texas Instruments Incorporated Overview 13

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

SLUSAP2B –MARCH 2012–REVISED JULY 2012 www.ti.com

2.8 Pin Functions

Additional pin functionality is specified in the following table.

Table 2-2. Pin Functions

ALTERNATE ASSIGNMENT PIN NAME PRIMARY ASSIGNMENT CONFIGURABLE NO. 1 NO. 2 NO. 3 AS A GPIO?

1 AGND Analog ground

2 AD13 12-bit ADC, Ch 13, Connected to comparator E, I-share

3 AD06 12-bit ADC, Ch 6, Connected to comparator F

4 AD04 12-bit ADC, Ch 4, Connected to comparator D

5 AD03 12-bit ADC, Ch 3, Connected to comparator B & C

6 DGND Digital ground

7 RESET Device Reset Input, active low

8 ADC_EXT_TRIG ADC conversion external trigger input TCAP SYNC PWM0 Yes

9 PMBUS_CLK PMBUS Clock (Open Drain) SCI_TX0 Yes

10 PMBUS_DATA PMBus data (Open Drain) SCI_RX0 Yes

11 DPWM0A DPWM 0A output Yes

12 DPWM0B DPWM 0B output Yes

13 DPWM1A DPWM 1A output Yes

14 DPWM1B DPWM 1B output Yes

15 DPWM2A DPWM 2A output Yes

16 DPWM2B DPWM 2B output Yes

17 DWPM3A DPWM 3A output Yes

18 DPWM3B DPWM 3B output Yes

19 PMBUS_ALERT PMBus Alert (Open Drain) Yes

20 PMBUS_CTRL PMBus Control (Open Drain) Yes

21 TCK JTAG TCK TCAP SYNC PWM0 Yes

22 TDO JTAG TDO SCI_TX0 PMBUS_A FAULT0 Yes

LERT

23 TDI JTAG TDI SCI_RX0 PMBUS_C FAULT1 Yes

TRL

24 TMS JTAG TMS Yes

25 FAULT2 External fault input 2 Yes

26 DGND Digital ground

27 V33D Digital 3.3V core supply

28 BP18 1.8V Bypass

29 AGND Substrate analog ground

30 AGND Analog ground

31 EAP0 Channel #0, differential analog voltage, positive input

32 EAN0 Channel #0, differential analog voltage, negative input

33 EAP1 Channel #1, differential analog voltage, positive input

34 EAN1 Channel #1, differential analog voltage, negative input

35 EAP2 Channel #2, differential analog voltage, positive input

36 AGND Analog ground

37 V33A Analog 3.3V supply

38 AD00 12-bit ADC, Ch 0, Connected to current source

39 AD01 12-bit ADC, Ch 1, Connected to current source

40 AD02 12-bit ADC, Ch 2, Connected to comparator A, I-share

14 Overview Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): UCD3138

UCD3138

www.ti.com SLUSAP2B –MARCH 2012–REVISED JULY 2012

3 Electrical Specifications

3.1 ABSOLUTE MAXIMUM RATINGS (1)

over operating free-air temperature range (unless otherwise noted)

VALUE UNIT

MIN MAX